## ALTO: A PLATFORM FOR OBJECT CODE MODIFICATION

by

Robert Muth

Copyright© Robert Muth 1999

A Dissertation Submitted to the Faculty of the DEPARTMENT OF COMPUTER SCIENCE In Partial Fulfillment of the Requirements For the Degree of DOCTOR OF PHILOSOPHY In the Graduate College THE UNIVERSITY OF ARIZONA

1999

## ALTO: A PLATFORM FOR OBJECT CODE MODIFICATION

Robert Muth, Ph. D. The University of Arizona, 1999

Director: Saumya K. Debray

This dissertation describes Alto, a platform for object code modification for Digital Unix/Alpha executables. Object code modification, also called binary rewriting, allows us to change compiled and linked programs, thereby extending the process of code generation well past the compilation phase of a program.

Object code modification is becoming increasingly important. One reason for this is the recent trend of making programs available as executables only — without the corresponding source code.

We explain the difficulties encountered by object modification, especially in the area of program analysis, and show how they are dealt with in Alto. Several improvements to register liveness analysis are presented.

Alto has been used to implement an optimizer which allows us to evaluate the benefits of classical compiler optimizations when applied to object code. This optimizer outperforms the vendor-supplied optimization tools significantly. Alto has also been used to instrument programs in order to generate sophisticated execution profiles, such as value profiles. We show how such profiles can be profitably exploited using a novel technique — guarded code specialization — and how this optimization can be incorporated into the optimizer.

Finally, we consider the issue of code compression, i.e., using Alto to make programs smaller rather than to make them faster. A variety of transformations are presented which are able to reduce the code size of programs substantially.

## STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at The University of Arizona and is deposited in the University Library to be made available to borrowers under rules of the Library.

Brief quotations from this dissertation are allowed without special permission. provided that accurate acknowledgment of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted bt the copyright holder.

SIGNED:

### ACKNOWLEDGEMENTS

Credit for much of the work described in this dissertation belongs to my tireless advisor, Professor Saumya Debray. He provided for an excellent research environment, left me enough freedom to do things the way I thought they should be done, and was always available to discuss ideas and problems.

I would also like to thank my committee members Peter J. Downey and William Evans for numerous helpful discussions and for their patients with revising early drafts of this document.

Other people that have worked on Alto also deserve my gratitude: Koen De Bosschere developed an early prototype of Alto. Bjorn De Sutter and Scott Watterson worked with me on the current version.

Last but not least I would like to thank my parents Guenther and Yvonne. They made the right decisions for my education when I was young, and later on provided moral support and encouragement when it was up to me to make decisions.

This work was supported in part by the National Science Foundation under grants CCR-9502826 and CCR-9711166.

## TABLE OF CONTENTS

| LIST OI | F FIGURI | ES                              | 9  |

|---------|----------|---------------------------------|----|

| LIST OI | F TABLE  | S                               | 11 |

| ABSTR   | ACT      |                                 | 13 |

| СНАРТ   | ER 1: IN | TRODUCTION                      | 14 |

| 1.1     | Motivati | ion                             | 14 |

| 1.2     | Related  | Work                            | 23 |

| 1.3     | Contribu | utions of Alto                  | 28 |

| СНАРТ   | ER 2: OV | /ERVIEW OF THE ALTO SYSTEM      | 30 |

| 2.1     | Parsing  |                                 | 31 |

|         | 2.1.1    | Code Discovery                  | 32 |

|         | 2.1.2    | Control Flow Graph Construction | 32 |

|         | 2.1.3    | Computed Indirect Jumps         | 36 |

|         | 2.1.4    | Control Flow Anomalies          | 36 |

| 2.2     | Editing  |                                 | 38 |

|         | 2.2.1    | Scale Problems                  | 38 |

|         | 2.2.2    | Self Modifying Code             | 40 |

| 2.3     | Code Ge  | eneration                       | 40 |

|         | 2.3.1    | Address Translation             | 41 |

|         | 2.3.2    | Segment Growing                 | 43 |

| CHAPTER 3: ANALYSES      |           |                                                             |    |

|--------------------------|-----------|-------------------------------------------------------------|----|

| 3.1                      | Register  | Liveness Analysis                                           | 45 |

|                          | 3.1.1     | Interprocedural Data Flow Analyses                          | 46 |

|                          | 3.1.2     | Interprocedural Register Liveness Analysis                  | 47 |

|                          | 3.1.3     | Improving the Precision of Register Liveness Analysis       | 58 |

| 3.2                      | Register  | Use-Def Chains                                              | 63 |

|                          | 3.2.1     | Algorithm                                                   | 64 |

|                          | 3.2.2     | Performance                                                 | 66 |

| 3.3                      | Register  | Alias Analysis                                              | 67 |

|                          | 3.3.1     | Alias Analysis by Inspection                                | 68 |

|                          |           |                                                             | 70 |

| CHAPTER 4: OPTIMIZATIONS |           |                                                             | 70 |

| 4.1                      | Experim   | ental Setup                                                 | 71 |

| 4.2                      | Optimiz   | ation of Constant Expressions                               | 72 |

|                          | 4.2.1     | Interprocedural Constant Propagation, Constant Folding, and |    |

|                          |           | Strength Reduction                                          | 72 |

|                          | 4.2.2     | Constant Generation                                         | 77 |

|                          | 4.2.3     | Constant Usage                                              | 80 |

|                          | 4.2.4     | Direct Execution                                            | 81 |

| 4.3                      | Instructi | on Elimination                                              | 83 |

|                          | 4.3.1     | Useless Instruction Elimination                             | 83 |

|                          | 4.3.2     | Move Elimination                                            | 84 |

|                          | 4.3.3     | Load and Store Avoidance                                    | 87 |

|                          | 4.3.4     | Unreachable Code Elimination                                | 89 |

| 4.4                      | Code Me   | otion and Restructuring Optimization                        | 92 |

|                          | 4.4.1     | Inlining                                                    | 92 |

|       | 4.4.2     | Code Positioning                                   | 94  |

|-------|-----------|----------------------------------------------------|-----|

| 4.5   | Overall   | Effectiveness                                      | 95  |

|       | 4.5.1     | Without Profiles                                   | 95  |

|       | 4.5.2     | With Profiles                                      | 96  |

| СНАРТ | 'ER 5: C  | OMMON CASE SPECIALIZATION                          | 100 |

| 5.1   | Prelimi   | naries                                             | 103 |

| 5.2   | Code S    | pecialization                                      | 104 |

|       | 5.2.1     | Estimating Costs and Benefits of Specialization    | 105 |

|       | 5.2.2     | Identifying Candidates for Specialization          | 107 |

|       | 5.2.3     | Value Profiling                                    | 108 |

|       | 5.2.4     | Carrying out the Specialization                    | 110 |

| 5.3   | Experin   | mental Setup                                       | 120 |

| 5.4   | Experin   | mental Results                                     | 120 |

| CHAPT | ER 6: C   | ODE COMPRESSION                                    | 126 |

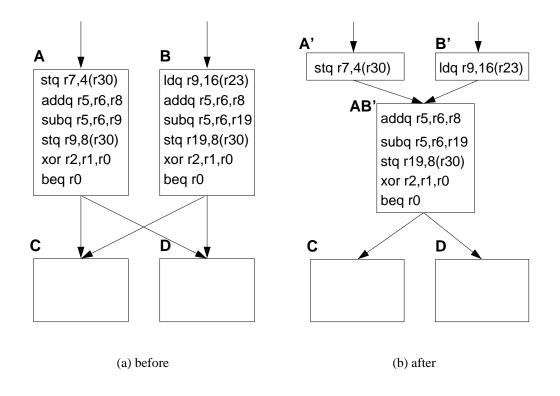

| 6.1   | Local F   | Factoring                                          | 130 |

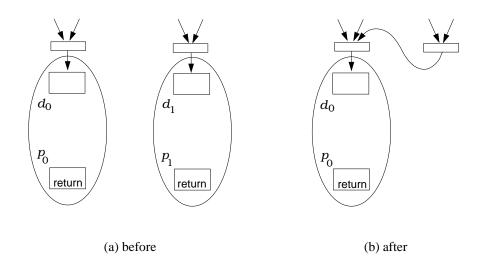

| 6.2   | Intrapro  | ocedural Tail Merging or Cross Jumping             | 133 |

| 6.3   | Proced    | ural Abstraction                                   | 134 |

|       | 6.3.1     | Procedural Abstraction for Individual Basic Blocks | 135 |

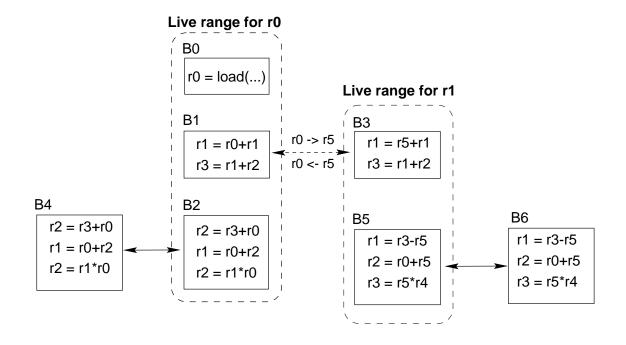

|       | 6.3.2     | Single-Entry/Single-Exit Regions                   | 139 |

|       | 6.3.3     | Architecture-Specific Idioms                       | 143 |

| 6.4   | Experin   | mental Setup                                       | 149 |

| 6.5   | Experii   | mental Results                                     | 150 |

| СНАРТ | 'ER 7: FI | UTURE WORK                                         | 152 |

| APPENDIX A: ALPHA MACHINE INSTRUCTIONS | 154 |

|----------------------------------------|-----|

| REFERENCES                             | 156 |

## LIST OF FIGURES

| 2.1 | Generic executable format                                       | 31  |

|-----|-----------------------------------------------------------------|-----|

| 2.2 | Modeling subroutine calls                                       | 35  |

| 2.3 | Use of compensation edges                                       | 37  |

| 2.4 | Translations of a C switch statement using a computed jump      | 42  |

| 3.1 | Unrealizable path in context insensitive analyses               | 47  |

| 3.2 | Unified fixpoint computation                                    | 53  |

| 3.3 | Code example: addition of complex numbers                       | 60  |

| 3.4 | Impact of enhancements to liveness analysis                     | 63  |

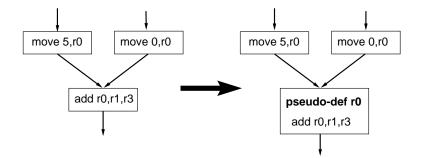

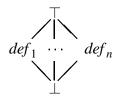

| 3.5 | Introduction of pseudo definitions                              | 64  |

| 3.6 | Example for alias analysis                                      | 69  |

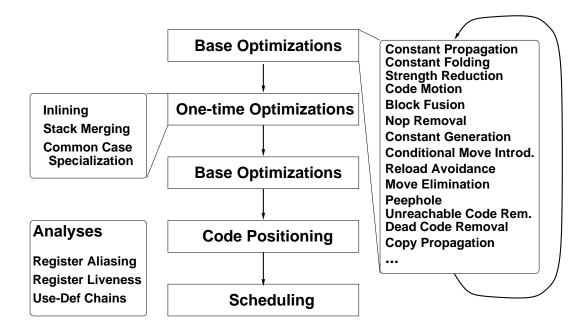

| 4.1 | Phases of the optimizer based on Alto                           | 71  |

| 4.2 | Code generated for $a = b + c$                                  | 78  |

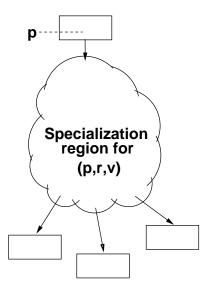

| 5.1 | Specialization region                                           | 111 |

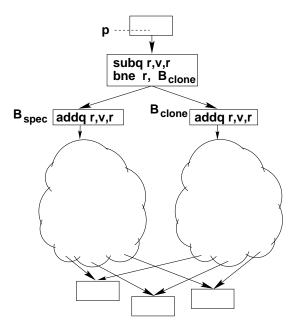

| 5.2 | Specialization transformation                                   | 114 |

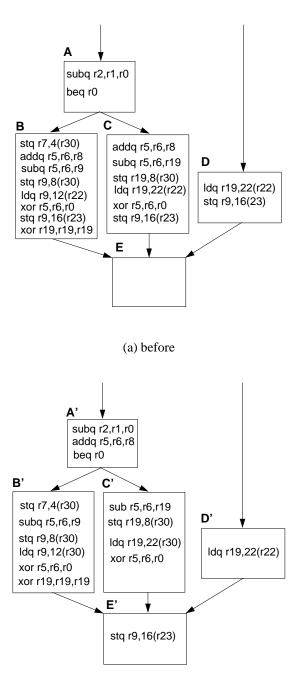

| 5.3 | Effect of value specialization on a node in m88ksim::killtime() | 116 |

| 5.4 | Unspecialized code fragment from m88ksim::align()               | 118 |

| 5.5 | Specialized code fragment from m88ksim::align()                 | 119 |

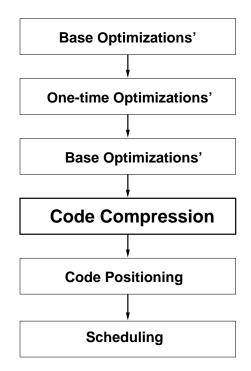

| 6.1 | Phases of the code compressor based on Alto                     | 127 |

| 6.2 | Local factoring                                                 | 131 |

| 6.3 | Cross jumping                                              | 133 |

|-----|------------------------------------------------------------|-----|

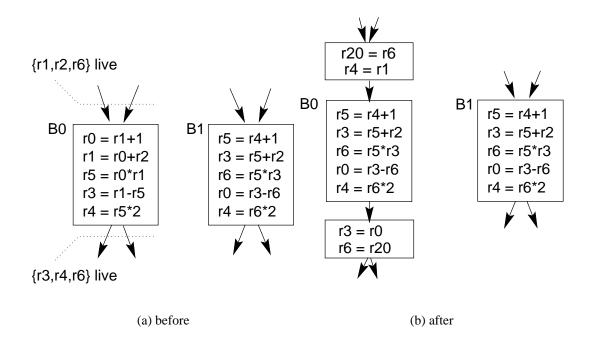

| 6.4 | Example of basic-block-level register renaming             | 136 |

| 6.5 | Interference effects in live-range-level register renaming | 138 |

| 6.6 | Merging regions ending in returns via cross jumping        | 142 |

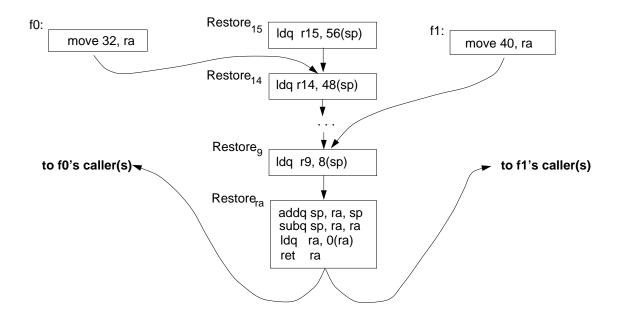

| 6.7 | Example for function prolog factoring                      | 145 |

| 6.8 | Example for function epilog factoring                      | 148 |

# LIST OF TABLES

| 2.1  | Characteristics of the SPECint95 benchmarks                 | 39  |

|------|-------------------------------------------------------------|-----|

| 3.1  | Performance of liveness analysis                            | 58  |

| 3.2  | Performance of use-def chains                               | 67  |

| 4.1  | Effectiveness of Constant Propagation                       | 75  |

| 4.2  | Execution time impact of constant propagation               | 76  |

| 4.3  | Execution time impact of constant generation                | 79  |

| 4.4  | Execution time impact of constant usage                     | 81  |

| 4.5  | Execution time impact of useless instruction elimination    | 84  |

| 4.6  | Execution time impact of move elimination                   | 87  |

| 4.7  | Execution time impact of load and store avoidance           | 89  |

| 4.8  | Effectiveness of unreachable code elimination               | 91  |

| 4.9  | Execution time impact of inlining                           | 93  |

| 4.10 | Execution time impact of code positioning                   | 94  |

| 4.11 | Overall execution time impact (without profiles)            | 96  |

| 4.12 | Overall execution time impact (with profiles)               | 99  |

| 5.1  | Extent of profiling and specialization                      | 121 |

| 5.2  | Code growth due to specialization                           | 122 |

| 5.3  | Execution time impact of value-profile-based specialization | 123 |

| 6.1  | Impact of code compression on code size                     | 150 |

| 62  | Impact of code compression on execution time | 151 |

|-----|----------------------------------------------|-----|

| 0.2 |                                              | 151 |

## ABSTRACT

This dissertation describes Alto, a platform for object code modification for Digital Unix/Alpha executables. Object code modification, also called binary rewriting, allows us to change compiled and linked programs, thereby extending the process of code generation well past the compilation phase of a program.

Object code modification is becoming increasingly important. One reason for this is the recent trend of making programs available as executables only — without the corresponding source code.

We explain the difficulties encountered by object modification, especially in the area of program analysis, and show how they are dealt with in Alto. Several improvements to register liveness analysis are presented.

Alto has been used to implement an optimizer which allows us to evaluate the benefits of classical compiler optimizations when applied to object code. This optimizer outperforms the vendor-supplied optimization tools significantly.

Alto has also been used to instrument programs in order to generate sophisticated execution profiles, such as value profiles. We show how such profiles can be profitably exploited using a novel technique — guarded code specialization — and how this optimization can be incorporated into the optimizer.

Finally, we consider the issue of code compression, i.e., using Alto to make programs smaller rather than to make them faster. A variety of transformations are presented which are able to reduce the code size of programs substantially.

## **CHAPTER 1**

## **INTRODUCTION**

### 1.1 Motivation

This dissertation is about direct modifications of object code. Such modifications may occur either at a very late stage during linking (link time) or after linking (post link time). Both approaches are quite similar: integrating modifications within the linker will simplify parsing of the code and might give access to slightly more information about the code, while changing object code after linking provides a very clean separation of responsibilities and does not require access to potentially proprietary linker source. In what follows we will not distinguish between the two approaches.

Traditionally, it is the task of the compiler or assembler to generate object code and it seems complex and cumbersome to change object code once it has been produced. Nevertheless, the number of applications where object code modification is successfully employed grows rapidly. This is partly due to the fact that computers are becoming powerful enough to cope with the often quite high resource demands of object code modification.

The following list describes the most popular applications of object code modification.

**Customization** Most software vendors ship software in executable form. Because of the high maintenance and testing cost there is a reluctance to produce more than one version of an executable for any one platform. To ensure that the software works

on all systems, the vendors aim their executables at the lowest common denominator of the architecture. However, the systems the software runs on might be quite different, their CPUs might have slightly different instruction sets, cache sizes, pipelines, functional units, even the number of CPUs might be different. Consider, for example, the Windows 95 operating system which runs on such different CPUs as: x486, Pentium, Pentium Pro, Pentium II, Pentium III, Pentium Celeron, AMD K6-2, AMD K6-3, Cyrix M-2, etc. However, there is only one version of this software available. As another example consider the Alpha family of CPUs which used to lack instructions for loading/storing individual bytes and words. Instead, instruction sequences were used to emulate these elementary operations. Recent members of the CPU family have load and store instructions for bytes. A typical software vendor will most likely compile his programs not using the new instructions to ensure that his software runs on all CPUs. Consequently, users with state of the art systems experience suboptimal performance.

Object code modification can help customizing a program by making use of new features of the CPU when those are present in a system without requiring recompilation or waiting for new compiler releases supporting these features.

Customization usually leads to faster programs. However, one could imagine a situation were the example above is reversed, and in which we are presented with executable code compiled for the latest member the Alpha CPU family. We want to run it on an old version of the CPU, no longer supported by the software vendor. We can use object code modification to replace all the instructions which load and store bytes or words with emulating instructions.

Customization can also be used in combination with profiling to tune a binary for common input data and program usage. Suppose a certain user mostly exercises the spell checker and the display rendering portion of a word processor. It would be beneficial to reorder those components within the program to reduce the likelihood that they conflict in the instruction cache. Furthermore, assume that this person almost exclusively uses the Times font in his word processor documents. Clearly, this will change the behavior of the display rendering code: certain branches will or will not be taken with higher probability and certain values will be more likely to populate certain registers. Adapting the display rendering code for this common case — possibly at the expense of slowdowns for the uncommon case (e.g., the Helvetica font) — might be greatly beneficial to this particular user.

**Binary Translation** Taking customization to the extreme, we can attempt to translate the object code to run on a different platform. A few such translators have been implemented commercially: FX ! 32 is a Windows NT/x86 to Windows NT/Alpha translator [15], Freeport Express is a Solaris/Sparc to Digital Unix/Alpha translator [71], VEST translates OpenVMS/VAX to OpenVMS/Alpha [70, 64], and mx translates Ultrix/Mips to Digital Unix/Alpha [70, 64].

Binary translation is also useful for the fast emulation of a new or fictitious platform before actual hardware is available, allowing compiler writers, for example, to test their code generator in advance.

Binary translation often requires a runtime software emulator for the source platform, in order to cope with code that is generated on the fly and which cannot be statically translated. A translation that falls back to an emulator for the source platform is called hybrid translation. The above mentioned FX!32 system actually uses emulation by default and will apply binary translation only to the frequently executed portions of a program in a separate offline step.

Translators can obviate the need for porting software if one is willing to pay the

price of a small performance penalty.

**Program Analysis/Profiling** Program analysis and profiling tools are the most popular applications for object code modification. Tools that instrument programs to determine basic block execution frequencies are very common. This information can be used by the compiler for profile-driven optimizations, by developers to help them focus their tuning efforts on the relevant parts of the code. Architects might use profiling to determine the dynamic instruction mix of applications or their data and instruction cache behavior [75, 47]. Other tools instrument the code to examine the accuracy of branch predictions or scheduling decisions made by the compiler without the use of special hardware (such as bus monitoring systems) or simulation. A common class of tools instrument object code to obtain address traces, which help architects improve cache design. These traces are very large, often consuming several gigabytes of disk space. Instead of writing them to disk and processing them offline, a recent trend adds the processing code to the object code and invokes it whenever a new piece of trace information would normally be written to disk. While the first approach typically causes the instrumented program to run about 100 times slower [49], the second approach reduces this slowdowns to a factor of 10 [66].

There are, of course, other ways of obtaining profiling information. One is to make the compiler instrument the code [38], and another is to use statistical methods [4]. Instrumenting code at a higher level than object code may not yield accurate information of the type computer architects care about, and it also critically changes the program behavior that we want to analyze (analogously to "Heisenberg's uncertainty principle" in physics). Statistical methods, on the other hand, sometimes have problems with accuracy. **Debugging** Object code modification also has a wide range of useful applications in debugging. Suppose that because of a programming error a memory cell is accidentally overwritten. Locating the point where the overwrite occurs can be a very difficult task. If there is no hardware support on the CPU we could resort to modifying the compiler to add checks, but this would be slow and libraries would not be covered. Another approach which has been used in the past and which is also rather slow is to single step through the program, continuously checking whether the memory cell has changed. A more efficient solution is to modify the object code to add checking code before each write instruction that will trap on a write to the memory cell in question.

Purify uses object code modification to detect memory leaks, out of bounds memory/array accesses, and use of uninitialized data [40].

JiTI, A debugging aid with a somewhat different flavor, inserts instrumentation code before load and store instructions in a parallel program which will assure that these loads and stores occur in a formerly observed order. This enables deterministic replays in (shared memory) parallel environments which is a great help in reproducing bugs [62, 61].

**Software Fault Isolation (Sandboxing)** Software fault isolation is closely related to the debugging techniques mentioned above. We describe a scenario from [72]: Suppose we have a piece of untrusted object code which we want to link with trusted code. One concern is that the piece of untrusted code might accidentally modify data structures maintained by the trusted code and hence corrupt the system. To address this problem we could assign the untrusted code to its own segment within the applications address space, and add checking code before each read/write instruction. The checking code will trap on a read/write attempt outside of the segment.

The overall effect is very similar to that which Java achieves with a combination of type checking and runtime checks.

Another application is the prevention of certain security attacks that exploit buffer overflows on the stack. Most attacks exploit buffer overflows inside the programs to (a) create a subroutine that spawns a root shell on the stack (b) overwrite the return address in the current stack frame with the start address of the newly created subroutine. We can prevent this attack by inserting checks before each indirect control transfer (jump, return), to validate that the address being jumped to lies in a valid range.

- **Code Optimization** Intuitively, code optimization should be the domain of the compiler, since it has access to high level information such as data types, control structures, alias information, etc., which greatly aids in generating efficient code and which is not readily available at the object code level. So why bother optimizing object code?

- We want to be compiler/language independent.

Working with object code makes our optimizations essentially compiler and language independent, similar to a common back end used with several front ends. However, we still may need to recognize certain compiler and/or language specific idioms at the object code level (like computed jumps) and treat them specially, in order to improve the effectiveness of the optimizations.

difficult. Hence, it is very popular to try out new optimizations in a simple and

We want to add a new optimization to a compiler.

Often we do not have access to the compiler source. Or, the documentation of the compiler source is so poor that adding the new optimization might be

well documented compiler like lcc [34] whose source is publicly available. However, it is questionable whether results obtained in this way will transfer to a production quality compiler. Applying optimizations at link time, on the other hand, allows us to essentially add optimizations to the best available compiler without modifying it.

• The program source or parts thereof (libraries) are unavailable.

Especially for old programs (legacy software), source code is often unavailable or it is unclear which version of the source corresponds to the program we want to optimize. Optimizing the object code appears to be the only way to improve performance of these programs.

• The optimization cannot be easily performed at compile time.

Consider the case where we want to improve the control transfer (jump) code for subroutine invocations. Depending on the distance of the jump (in number of bytes), different jump instructions can be chosen, a pc-relative jump with short displacement, a pc-relative jump with long displacement, or an absolute jump. Unfortunately, the compiler is usually not able to estimate the jump distance, and hence needs to pick the most conservative and hence suboptimal instruction, viz. the absolute jump. At link time, on the other hand, we know exactly what the jump distance is and can pick the optimal instruction.

• We want to perform whole program optimization.

Whole program optimization can, in theory, be done at compile time but this is often hindered by missing source for library code. This problem does not exist for statically linked object code.

• We want to utilize profiling information obtained at the object code level. Generating profiling information by instrumenting object code is very popular and, because of tools like Atom (cf. 1.2), also fairly easy. The problem is to exploit this information in an optimizing compiler. There is an "impedance mismatch" between the information provided by the object code level profiling and the source level compiler. This "impedance mismatch" problem is also found in a source level debugger. Such a debugger actually works at the object code level, but needs to back map the information to source code. This is a hard problem — especially when the code is highly optimized. When optimizing at the object code level, on the other hand, the mapping is one-to-one and does not present any problems.

**Code Compression/Compaction** While the cost metric we tried to reduce in the previous cases was time, we may also be concerned about space. Besides classical optimizations which usually also reduce code size, we can reduce code size using special compression techniques. Compressed code must either be decompressed before execution (called wire representation) [31] or it can be executed without decompression [35, 21]. The first method results in a smaller compressed representation than the second, but requires the overhead of decompression before execution. This overhead may be negligible and in fact maybe compensated for by the savings in transmission or retrieval cost. A more severe problem, however, is that it requires space for the decompressed code.

The second method preserves executability of the code and is therefore more amenable to object code modification even though the borders between the two methods are somewhat flowing. If we prepend a piece of code to the wire representation that first performs decompression and then runs the decompressed executable, we have technically preserved executability. Tools like this were very popular when computers were not equipped with hard disk drives and one tried to cram as much information as possible onto floppy disks [59].

It is also possible to add some sort of interpretive techniques to an executable to reduce space requirements. For example, on the Motorola 68000 based Atari ST computer the designers were not able to fit the entire operating system into the 192 kB ROM. So they replaced common opcode sequences with illegal instructions <sup>1</sup> and installed an interpretor to handle the illegal instruction exceptions [42].

A similar but less system specific mechanism factors common code sequences into subroutine calls [35, 27, 21]. This can in principle be done by a compiler but often the intermediate representations used in the compiler do not provide enough support for this kind of transformation. In addition, more of the code is visible at link time, e.g., libraries, increasing the number of opportunities for factoring.

This dissertation describes Alto (A Link Time Optimizer), a platform for modification of object code. Alto has been implemented for Digital Unix/Alpha executables and is being ported to Linux/Alpha. The main emphasis of the dissertation will be on object modification for optimization, code compression, and profiling.

Despite being a fairly system specific piece of software, the experience gained with Alto should be transferable to other platforms/architectures (especially RISC based systems) since the Alpha is a very generic RISC CPU. In fact, its instruction set is very similar to low level code representations such as ILOC [58], LIR [55], and Omnicode [73, 1] so that Alto could also be viewed as a backend for monolithic compilation.

<sup>&</sup>lt;sup>1</sup>The illegal instructions were taken from a pool of reserved opcodes called "line-f" because the first hexadecimal digit of each opcode was "f". Later those opcodes became legal floating point instructions and the scheme was abandoned.

## 1.2 Related Work

This section describes other projects in the area of object code modification and points out their differences from Alto.

#### OM

OM is an optimizer for executables initially implemented for DEC-stations running Ultrix/Mips, and later ported to Digital Unix/Alpha.

OM was designed as a separate pass after linking but, unlike Alto relies on the linker to provide additional information not found in the executable. OM can also make use of profiling information [67, 68].

One of the design goals for OM has been to make it fairly light-weight. Compared to Alto, it does not perform many optimizations, and the ones it does perform are restricted to those that do not consume a lot of resources. The following is a list of optimizations performed by OM:

- Code size reduction by unreachable code removal

- Compaction of the memory area that holds compile time constants by elimination of unused and duplicate constants

- Reordering of global data structures (variables) to provide more efficient access

- Profile guided code positioning and alignment

- Instruction (re-)scheduling

- Peephole optimization

- User-directed procedure inlining

#### ATOM

Atom (Analysis Tool with OM) is an instrumentation tool generator for the Digital Unix/Alpha platform which originated in the OM project but has since then diverged. Atom is a very mature and user-friendly tool which is used extensively inside DEC (now COMPAQ). It has been used for many big applications including OS kernels [66].

Atom strictly separates the tool specific part from the common infrastructure needed by all tools. The tool specific part consists of an analysis component and an instrumentation component. Both components can be written entirely in a high level language (typically C), which distinguishes Atom from any other tool, including Alto.

The instrumentation code is linked with the Atom instrumentation engine to create an instrumentation tool. This tool will parse an executable and insert function calls at specific places via the Atom API. The functions called are those defined in the analysis code. Calls to these functions can be inserted before/after program execution, shared library loading, procedures, basic blocks, or instructions. The parameters passed to the functions are determined by the instrumentation code. Possible parameters are: current register values, instruction fields, symbol names, addresses, etc.

Atom even allows the analysis code to dynamically allocate memory. This is nontrivial because memory allocated by the analysis code should not be visible to the instrumented program in order to preserve program behavior as much as possible, i.e., the values returned by calls to malloc() should be the same in the original and in the instrumented version of the program.

Registers modified by an analysis routine are saved to the stack and later restored. Some attempts are made to reduce this overhead but it is still quite significant. Programs instrumented using Atom/pixie (see below) typically suffer a slowdown of a factor of 2 to 3. Among the tools that have been (re-)implemented with Atom are:

- pixie. A reimplementation of a basic block execution frequency profiling tool. The profile generated by pixie is used by OM to guide some of its optimizations [69, 75].

- Third Degree. A memory leak detection tool.

- Hiprof. A performance analysis tool that collects data similar to, but more accurate than, gprof.

### SPIKE

Spike is an adaptation of OM to the Windows NT/Alpha platform. Spike consists of an instrumentation part and optimization part. Both are embedded in the Spike optimization environment (SOE), which transparently handles the task of collecting and managing profiling information for the user [18, 17, 36].

Spike is aimed at call intensive programs, with loops that span multiple procedures and procedures that have complex control flow and contain numerous basic blocks.

The instrumentation part is a pixie adaptation which provides basic block and control flow edge execution frequency counts. A minimum of basic blocks and edges are instrumented and register liveness analysis is used to find free scratch registers for the instrumentation code. The instrumentation code bloat is thereby only 30%. There are plans to replace the instrumentation part by statistical sampling using DCPI [4].

Spike automatically scans the executable for the dynamically linked libraries (DLLs) it uses and processes them as well.

The important transformations performed by the optimization part are profile-driven:

• Pettis-Hansen style profile guided code placement [57] improves instruction cache performance.

• Hot cold optimization (HCO) reduces the length of the most frequently executed paths in a procedure.

Spike reportedly speeds up program execution by as much as 33%, which seems to be mostly due to the profile guided code placement. The HCO optimization benefit is unclear since no execution time improvements are reported. Spike seems to be most effective with call intensive programs. Programs that spend a significant amount of time in inner loops, e.g., FORTRAN programs, usually get very little speedup. Compared to Alto very few optimizations have been implemented.

#### EEL

EEL (Executable Editing Library) is a C++ library that tries to hide much of the complexity and system specific detail of editing executables. It was developed at the University of Wisconsin-Madison and runs on Solaris/Sparc and Ultrix/Mips. [48]

EEL tries to be as system and machine independent as possible. Theoretically, tool builders should be able to modify an executable without being aware of the details of the underlying architecture or operating system, or being concerned with the consequences of deleting instructions or adding foreign code. EEL's programming interface is not as high level as Atom's but the programmer has more control over the instrumentation process since Atom can only insert subroutine calls and not modify existing instructions. As an intermediate representation EEL employs a machine independent RISC-like abstract instruction set. However, instrumentation code (called snippets) consists of concrete instructions that must be rewritten in machine language for different architectures. A register scavenging scheme that takes advantage of calling conventions is used to provide the scratch registers for the snippets, and to reduce the amount of register spilling. Hence the snippet defined by the tool writer and the actual code added as instrumentation

to an executable might differ in the allocation of registers. If other changes are wanted, e.g., adjustments of offset/displacements, the tool writer needs to back-patch the snippet just before it is added to the binary. The number of instructions is not allowed to change at this point.

EEL does not use relocation information and falls back to runtime code when static analysis is insufficient. This also prevents the user from editing certain basic blocks (typically 15-20% of all basic blocks) which are excluded from instrumentation. The authors claim that in most case alternative basic blocks can found and edited instead. For this reason EEL is a instrumentation platform rather than optimization platform.

EEL has been used to reimplement the qp and qpt tools [8] which are used to obtain path profiles.

#### Etch

Etch is a binary modification tool for Windows NT/x86 executables. It was developed jointly at the University of Washington and Harvard University and its architecture was strongly influenced by Atom. Like Atom it separates instrumentation from analysis. To instrument a program, Etch is invoked with the name of an executable and a dynamically linked library (DLL). The DLL contains the analysis code in the form of callback functions that are invoked by Etch to modify the executable. Those functions can in turn call the Etch API to perform the actual instrumentation [60].

Etch includes a runtime library with the modified executable which might make it less suitable for optimizations. The only reported optimization is code layout based on the Pettis-Hansen algorithm [57]. Like Spike it can handle dynamically linked executables and will instrument/optimize DLLs used by a program.

### **1.3** Contributions of Alto

Alto has been implemented in the C programming language and works reliably on all programs tested. The software can be downloaded free of charge from the Alto webpage http://www.cs.arizona.edu/alto/.

The main contributions are listed below.

1. Program analysis (Section 3)

We present several improvements to register liveness analysis. We show how to preserve correctness of the analysis in the presence of control flow anomalies typically not encountered in high level languages but frequently observed in object code. A novel insight about the fixpoint equations for the analysis is exploited to speed up its computation time by 25%. We also show how the consideration of calling conventions and callee saved registers decreases the number of live registers. Furthermore, We examine space-time tradeoffs and space/time-precision tradeoffs.

2. Classical compiler optimizations (Chapter 4)

We evaluate the usefulness of an extensive set of classical compiler optimizations in the context of link time code modification. Common sense suggests doing classical compiler optimization in the compiler. However, we find significant optimization opportunities at link time. Programs optimized with our system typically run 6% faster than those produced with the vendor-supplied compiler infrastructure alone.

3. Common case specialization (Chapter 5)

We discuss guarded code specialization, a new optimization based on value profiles, which could also be incorporated into ordinary compilers. We show how to select program points for value profiling and present a cost-benefit analysis to automatically determine which of those program points are to be specialized for what value. Guarded code specialization results in an additional speedup of up to 10% for some programs.

4. Code compression (Chapter 6))

We examine opportunities for code size reduction via object code modification. Using code factoring transformations on top of classical compiler optimizations, we are able to reduce code size by 38% on the average.

## **CHAPTER 2**

## **OVERVIEW OF THE ALTO SYSTEM**

Object code modification is a three phase process consisting of :

- Parsing transformation of the object code into an intermediate representation

- Editing manipulation of the intermediate representation

- Code Generation transformation of the intermediate representation back into object code

In this chapter we will discuss these phases, describe the common problems encountered, and show how Alto handles them.

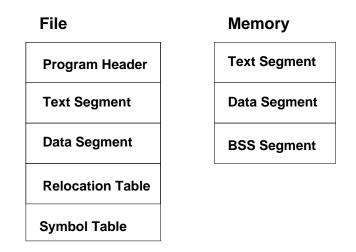

We assume a generic Unix executable format depicted in Figure 2.1 [39]. Besides the file representation, the runtime organization in memory is also shown.

The Program Header contains offsets and sizes of the segments and tables and their location in the address space. It also contains the code address where execution starts. The Text Segment contains read-only data, i.e., the program code and constants. The Data Segment contains initialized data that is read/writable. The BSS Segment contains zero initialized read/writable data and is therefore reduced to an address/size pair in the file representation. The Relocation Table contains information which allows us to change the program to run at different absolute positions in the address space. The Symbol Table contains information traditionally used by a debugger to establish a correspondence

between the source code and the object code derived from it. The symbol table is optional and can be removed from the executable using the strip command. If present, Alto will use it to make its output more user-friendly. For example, instead of reporting that "the subroutine at address 0x120003ac has been inlined", the message "subroutine memcpy has been inlined" will be printed.

Figure 2.1: Generic executable format

## 2.1 Parsing

The task of parsing is to transform the object code into some intermediate form which is more suitable for further modifications.

Alto is using a three-address intermediate language that is very close to the Alpha machine language [2]. Although this might seem to make Alto very non-portable, this three address code is in fact very similar to the low level intermediate representation used in many compilers [54, 55, 58].

#### 2.1.1 Code Discovery

Code discovery tries to locate the parts of the object file that contain executable instructions. Locating code is not always straightforward. Often read-only data (string constants, jump tables, floating point constants) and program code are interleaved in the Text Segment. This problem is aggravated if the architecture has variable length instructions (like the Intel x86 architecture). In this case one has to be very careful where to start decoding instructions. Usually one has to couple code discovery with control flow graph construction, i.e., whenever a new branch target is identified one starts decoding instructions at that address until one encounters a control flow changing instruction. In the presence of indirect jumps, however, it might still be impossible to discover all code.

Fortunately, on the Digital Unix/Alpha platform, compilers are very disciplined and place code and data into separate areas of the Text Segment. Furthermore all instructions are 32 bits wide.

If the program is dynamically linked, code discovery may also try to identify the shared libraries used by the program and to parse them as well. Alto currently does not support dynamically linked code.

#### 2.1.2 Control Flow Graph Construction

An important part of the intermediate representation is the control flow graph, which is also essential for the dataflow analyses performed during subsequent phases.

Conceptually, an executable consists of a set of subroutines (functions) denoted as *Functions*. The distinguished subroutine *entryfun* designates where the execution of the program begins. Each subroutine f consists of a collection of nodes (basic blocks) *Nodes*[f]. A node n consists of a sequence of instructions *Instructions*[n], in which control always enters at the beginning and leaves at the end without intervening branches.

The first instruction of a node is also called *leader*. The collection of all the basic blocks in all subroutines is denoted as *Nodes*. To simplify reasoning about nodes we assign types to them, denoted by Type[n]. There is a wide variety of types. The most relevant ones are: *call* for those nodes that initiate a subroutine invocation, *return* for those nodes where execution resumes after the subroutine call, *init* for those nodes starting a subroutine, *exit* for those nodes ending a subroutine. Each subroutine *f* has exactly one node of type *init* denoted as *InitNode*[*f*] and exactly one node of type *exit* denoted as *ExitNode*[*f*].

Nodes are connect by directed edges, indicating possible control flow. An edge might connect two nodes within the same subroutine — in which case it is called an intraprocedural edge — or two nodes in different subroutines — in which case it is called an interprocedural edge. The collection of all edges is denoted as *Edges*. The set of immediate successor (resp. predecessor) nodes of a node *n* is denoted *Succ*[*n*] (resp. Pred[n]).

An interprocedural control flow graph consists of the directed graph created by *Nodes* and *Edges*. It is very similar to the program supergraph described in [56]. The (intraprocedural) control flow graph for subroutine f is the subgraph of the control flow graph induced by *Nodes*[f].

Creating control flow graphs for programs in high-level languages is straightforward [2]. Matters are somewhat more complex at link time because control flow has been obscured by the compilation process, and because we need to deal with machine-level idioms for control transfer such as computed jumps. The algorithm used by Alto to construct a control flow graph for an input program is as follows: As starting points we use all the Text Segment addresses appearing as literal data somewhere in the object code file. Here, relocation information helps us differentiate between real addresses and random bit patterns that just look like addresses. Included with those addresses is the start address of *entryfun* which can be found in the program header.

Now the "standard" algorithm [2] is used to identify more leaders and basic blocks. A leader that is reached by a call instruction begins a subroutine *init* node. <sup>1</sup> A function is assumed to extend from one *init* node until just before the next *init* node, in instruction sequence order. This ensures that each subroutine has exactly one *init* node. The assumption that control enters a subroutine at exactly one point and leaves at exactly one other point is occasionally violated resulting in irregular interprocedural control flow which our analyses and optimizations need to cope with. Section 2.1.4 describes how the introduction of compensation edges can support analyses and optimizations in that case.

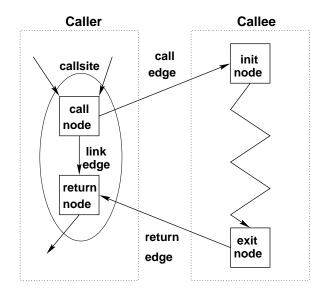

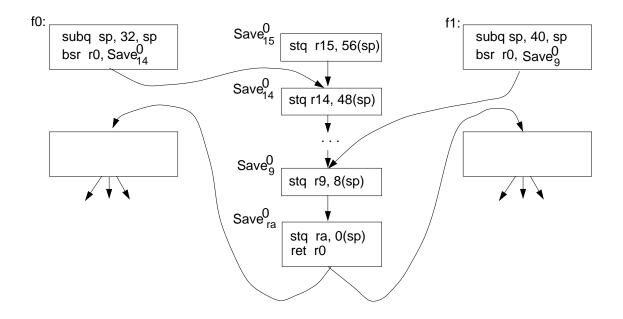

Next edges are added to the control flow graph. Subroutine calls are modeled as depicted in Figure 2.2. A *call* edge leads from the basic block containing the call instruction (*call* node) to the target block which is, by definition, a subroutine *init* node. A *link* edge connects the *call* node to the basic block beginning right after the call instruction (*return* node). A return edge leads from the *exit* block of the called function (callee) to the *return* node.

For any call node  $n_c$ ,  $ReturnNode[n_c]$  denotes the corresponding return node and  $Callee[n_c]$  denotes the function being called. Similarly, for any *return* node  $n_r$ ,  $CallNode[n_r]$  denotes the corresponding *call* node and  $Callee[n_r]$  denotes the function that was called.

<sup>&</sup>lt;sup>1</sup>Some of the leaders determined by literal addresses also mark function init blocks and this can be determined using the relocation information.

Figure 2.2: Modeling subroutine calls

Unconditional branches are eliminated from the intermediate representation since this information is implicit in the edges.

Whenever an exact determination of the target of a control transfer is not possible, Alto estimates the set of possible targets conservatively, using a special node *unknownnode* and a special subroutine *unknownfun*.<sup>2</sup> This simplifies the implementation of data flow analyses because we can associate worst-case data flow assumptions with them and otherwise treat them as ordinary nodes and subroutines. If there is an indirect jump to an unknown target we add an edge from the jump block to *unknownnode* and if there is an indirect call to an unknown subroutine it is simulated by a call to *unknownfun*. Conversely, if the start address of a block appears as literal data somewhere in the object code file, we assume it can be the target of any indirect jump and add an edge from *unknownnode* to the node. If the start address of a subroutine *init* node

<sup>&</sup>lt;sup>2</sup>*unknownnode* also represents the *init* and *init* node of *unknownfun*.

appears as literal data somewhere in the object code file we assume the subroutine can be the target of an indirect call and simulate a call from *unknownnode*.

## 2.1.3 Computed Indirect Jumps

Alto works hard to find the actual target of indirect jumps and calls and will adapt the control flow graph accordingly. As described in the previous section, a jump with a unknown target will initially be modeled as a jump to *unknownnode*. Alto tries to determine whether such a jump is a computed jump derived from a C switch statement (or similar construct in other languages) by pattern matching a code template with the code surrounding the jump. <sup>3</sup> The pattern matching is non-trivial since the compiler might have reordered instructions, peephole-optimized instructions, or moved instructions into different nodes. If we find a match, we have implicitly determined the location and dimension of the jump table and can refine the control flow graph by replacing the edge to *unknownnode* with edges to the actual target nodes.

This transformation is done as part of the editing phase because it greatly benefits from other transformations and analyses, such as liveness analysis.

#### 2.1.4 Control Flow Anomalies

Machine code is not as well behaved as high-level source code. In particular certain assumptions about control flow, which seem reasonable at a higher level, are routinely violated at the machine code level.

One assumption is that control leaves a subroutine only at its *exit* node or its call sites. At the level of executable code, this assumption can be violated by *escaping branches*, i.e., ordinary (non-subroutine-call) control transfers from one subroutine into another.

<sup>&</sup>lt;sup>3</sup>The template was derived by inspecting switch statement code produced by various compilers

Typical causes for *escaping branches* are tail call optimization and code sharing in handwritten assembly code (found, for example, in some numerical libraries).

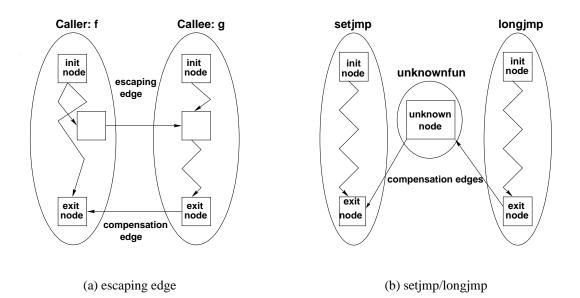

Another assumption is that a subroutine call returns to its caller at the instruction immediately after the call instruction. This assumption is violated by non-local control transfers via subroutines such as setjmp and longjmp.

Alto handles both cases by the inserting additional edges, called *compensation edges*, into the control flow graph as depicted in Figure 2.3.

Figure 2.3: Use of compensation edges

In the first case, an *escaping branch* from a caller subroutine f to a callee subroutine g results in a single compensation edge from the *exit* node of g to the *exit* node of f. Conceptually, this ensures that control flow entering f can also exit from f — this is important for the data flow analyses to safely approximate program behavior. Without the escape edge, data flow facts cannot be propagated back to f where they originated.

In the second case, the subroutine setjmp has a compensation edge from

*unknownnode* to its *exit* node, while the subroutine longjmp has a compensation edge from its *exit* node to *unknownnode*. This models the fact that the location of an invocation of setjmp can later be jumped to from unknown places, and that calling longjmp will cause a jump to an unknown location. Again this is necessary to insure a safe approximation for data flow analyses.

Some of the *escaping branches* can be avoided by duplicating code. We may choose to do this during the editing phase if the resulting code growth is reasonable.

## 2.2 Editing

In the editing phase the intermediate representation is transformed to achieve the desired goal, e.g., instrumentation, optimization, or code compression.

The following chapters present a variety of concrete transformations and the analyses necessary to support them. Here we will only discuss issues of a more general nature.

In Alto we restrict ourselves to changing code and code-related pieces of data like jump tables. The data portion of the program is left unchanged. The reason for this is that most high level information necessary to make correct transformations within the Data Segment is either lost during compilation or is extremely hard to recover. For example, we are not able to change the orders of variables in a structure or record.

### 2.2.1 Scale Problems

Figure 2.1 summarizes the basic characteristics of the SPECint95 benchmark suite [65], which are used in most of the experiments in this thesis. The benchmark programs were statically compiled, and hence the numbers include library subroutines.

| Benchmark | #Instructions | #Edges | #Nodes | #Subroutines |

|-----------|---------------|--------|--------|--------------|

| compress  | 18759         | 9224   | 5021   | 224          |

| gcc       | 295096        | 158723 | 77505  | 2130         |

| go        | 71721         | 29454  | 15696  | 605          |

| ijpeg     | 54611         | 21532  | 11534  | 639          |

| li        | 34768         | 17225  | 9138   | 646          |

| m88ksim   | 46117         | 21940  | 11473  | 528          |

| perl      | 90318         | 44997  | 22662  | 618          |

| vortex    | 127383        | 58107  | 28465  | 1026         |

Table 2.1: Characteristics of the SPECint95 benchmarks

As can be seen from the table, some benchmarks are quite big, e.g., gcc has about 300,000 instructions. Its intermediate representation in Alto consumes almost 100MB. Hence, any algorithm applied during the editing phase must be aware of the potentially huge size of the intermediate representation. Algorithms that work well in conventional compilers (which operate on a per module or per subroutine basis) might be impractical for object code modifications because of the high time and especially the high space complexity. Clearly, any algorithm that is quadratic in the number of instructions will not be feasible. Stingy algorithms — preferably linear in both time and space — are necessary. Often we will be forced to make tradeoffs between precision and efficiency. Furthermore, memory locality of the algorithms and data structures significantly influences performance.

#### 2.2.2 Self Modifying Code

Self modifying code and runtime generated code are a major hurdle to object code modification. Self modifying code had become somewhat out of fashion but is now gaining popularity again either directly [30, 29] or indirectly for just-in-time compilation [33].

Alto can cope with some forms of self modifying code, but will not work under all circumstances. Imagine a piece of code A in the Text Segment which is changed at runtime by another piece of code B. Note that this violates the read-only character of the Text Segment <sup>4</sup>. If we change A in the editing phase the assumptions made by B about Amight not be valid anymore. This could cause the program to work incorrectly.

However, in the more likely case that code is generated on the fly into a dynamically allocated piece of memory there will be no problems. The code cannot be altered by Alto since it is not part of the Text Segment. Invocation of such code will look like an indirect control transfer. This control transfer is safely modeled using *unknownfun*, making worst case assumptions about the runtime behavior of the code.

## 2.3 Code Generation

After the transformations on the intermediate representation are finished, we need to generate a new version of the executable. Converting the three-address code back into machine instructions does not pose any problems. Adding the unconditional branches that have been removed during parsing is also straightforward. The difficult part lies in translating the old code addresses into new ones and dealing with changed segment sizes.

<sup>&</sup>lt;sup>4</sup>Unfortunately, the programmer can use system calls to change access restrictions for segments

#### 2.3.1 Address Translation

The problem of address translation is a consequence of the fact that, after object code modification, code addresses (in particular subroutine start addresses) will have changed. Address translation has historically been a major problem for object code modification systems. Several solutions have been proposed and implemented [75].

One approach is to avoid the problem by allowing only transformations that do not change code addresses, e.g., old code can not be deleted or new code inserted. We are allowed only to substitute code, e.g., substitute an instruction with an unconditional branch to a piece of code which executes the original instruction and after doing some extra work branches back. Clearly, this approach is only useful for instrumentation but it can be used to instrument a running program [61] in its address space, while it is running.

The second approach translates some addresses statically and others dynamically, viz. at runtime. Pc-relative branches and subroutine calls are easily handled statically; so are branches and subroutine calls to absolute addresses. Targets of these branches and procedure calls are, by definition, basic block beginnings. Therefore all the system has to do is to remember, for each basic block, the original address. After code generation the new addresses of the basic blocks are also known, and we can translate old addresses to new addresses. Other control transfer instructions, i.e., indirect control transfers, are handled by runtime address translation. Here a code snippet is added before an indirect control transfer (jump) which, with the help of an additional table, translates old addresses into new addresses at runtime. The table is an array of new addresses indexed by old addresses, and is appended to the Text Segment. If the snippet cannot find an address in the table, it leaves it unchanged. This will allow runtime generated code to work properly. This approach is not well suited for optimizing executables, but has been used for instrumentation [75, 47]

The third approach — the one used by Alto — does all the address translation statically. This approach makes the assumption that indirect control transfers will branch to addresses that have ultimately been loaded (verbatim) from memory. Hence all the static translator has to do is to find the memory locations containing code addresses and replace them with the corresponding new address. These memory locations — which might be in the Text Segment, Data Segment or Program Header — are identified using relocation information. This approach relies on the compiler to avoid certain coding styles that would break the scheme. For example, consider the two translations of a C switch statement using a computed jump in Figure 2.4. <sup>5</sup>.

| .text  |                   | .data                   |

|--------|-------------------|-------------------------|

| lda    | r1, table         | targets:                |

| addq   | r1, r0, r1        | .word targetA, targetB, |

| jmp    | (r1)              | targetC                 |

|        |                   | .text                   |

| table: |                   | lda r1, targets         |

| br     | targetA           | addq r1, r0, r1         |

| br     | targetB           | ldq r1, 0(r1)           |

| br     | targetC           | jmp (r1)                |

| (a) b  | ad implementation | (b) good implementation |

Figure 2.4: Translations of a C switch statement using a computed jump

The value which is switched upon resides in register r0. The targets of the switch statement are the labels targetA, targetB, and targetC (not shown). The left

<sup>&</sup>lt;sup>5</sup>The meaning of the Alpha machine instructions is explained in Appendix A

hand side solution (a) adds the value of r0 to the table address to obtain the target of the indirect jump. The indirect jump is followed by an unconditional branch to the final destination. The right solution (b) adds the value of r0 to the address of a table containing the possible jump targets, then loads the target address and jumps to the final destination directly.

While there are no problems with the right hand side solution (b), the left hand side solution (a) will not work, because the target of the computed jump is the result of an arithmetic computation (rather than an indirect reference). Alto has no way of telling that the table of unconditional branches is part of a computed jump, and should there-fore remain unchanged. In fact, Alto removes all unconditional branches from its intermediate representation and instead maintains them as edges in the control flow graph. The resulting empty nodes may be moved around and possibly merged with other non-empty nodes.

#### 2.3.2 Segment Growing

Object code modification will usually change the size of the Text Segment. This is not a problem if the size shrinks, since we can pad it to the original length. However, if the size grows beyond the original size (because of, for example, inlining or instrumentation), the end of the new Text Segment may overlap the beginning of the Data Segment in the address space, forcing us to move the Data Segment and the BSS Segment to higher addresses. This can be achieved statically by using relocation information to identify all memory locations containing addresses inside the Data Segment or BSS Segment and updating them accordingly. Or, it can be achieved dynamically, by inserting code before all load and store instruction to update the load/store address if necessary. Luckily, under Digital Unix/Alpha, there is usually a very big gap between the end of the Text Segment

and the beginning of the Data Segment, <sup>6</sup> which eliminates the problem. The growth of the Text Segment might not exclusively stem from code growth: we also need extra space for new read-only constants and jump tables. For instrumentation purposes we might also want to increase the size of the Data Segment to make space for profiling counters. Again, because of the gap between the Text Segment and Data Segment under Digital Unix/Alpha, this can be easily accomplished by growing the Data Segment toward lower addresses and placing the extra data structures before the original Data Segment.

<sup>&</sup>lt;sup>6</sup>The Text Segment typically start at 0x12000000, and the data segment at 0x14000000.

# **CHAPTER 3**

# ANALYSES

In this chapter we describe techniques, analyses, and data structures used by Alto which are useful independently of the purpose of object code modification. The main focus is on register liveness analysis, which will provide the necessary scratch registers for many transformations performed during the editing phase.

## **3.1 Register Liveness Analysis**

Liveness analysis attempts to determine whether a value kept in a variable or storage location may be used later on during program execution. A variable is said to be *live* if this is the case. Liveness analysis of variables is a well-understood technique employed by most compilers to guide optimizations such as useless code elimination and register allocation [55]. Liveness analysis can also be performed on object code if we let registers take the place of variables. Its main purpose is to identify useless code and to provide scratch registers for the transformations performed during the editing phase.

Compared to traditional variable liveness analysis which is usually intraprocedural, the register liveness analysis for executable code presented here will be interprocedural. Interprocedural analysis on registers is simplified by the fact that there is no aliasing between registers and the number of registers for any given processor is bounded by a constant. What makes it difficult are control flow anomalies (cf. Section 2.1.4) and scale issues (cf. Section 2.2.1).

**Related Work:** Work most closely related to our own has been done by Srivastava and Wall on the OM optimizer [67] and by Goodwin on the Spike optimizer [36]. We improve on their liveness analysis in three ways. Firstly, we have changed the underlying flow equations resulting in three sets of almost identical equations, which simplifies implementation and reasoning about correctness. Secondly, we accelerate the fixpoint iteration by exploiting a novel insight about the interdependence of the various pieces of data flow information. This idea is also applicable to liveness analysis of variables. Thirdly, we show how to reduce the space requirement of the analysis by recomputation and exploitation of the new data flow equations.

Furthermore, we explore ways to improve the accuracy of liveness analysis. For a known technique involving callee-save registers we point out a possible generalization.

#### 3.1.1 Interprocedural Data Flow Analyses

Intraprocedural data flow analyses consider all possible paths in the control flow graph of a subroutine to give an estimate of what data flow facts hold at a given node. Conditionals are not interpreted, i.e. we assume that both sides of the branch can always be taken. As a result, we may include paths that will never be executed in reality and the estimate will be somewhat conservative.

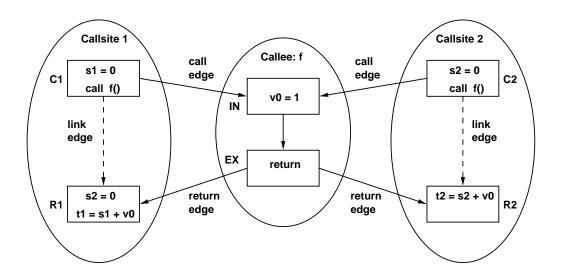

For interprocedural data flow analyses we can simply adopt the intraprocedural approach and regard the interprocedural control flow graph as one big ordinary control flow graph, treating *call* and *return* edges as regular edges and ignoring *link* edges. Analyses performed in this fashion are called *context insensitive* interprocedural analyses. Such analyses are simple and fast but often yield rather conservative estimates since many paths in the interprocedural control flow graph do not reflect real program executions. An example is shown in Figure 3.1 where two call sites call the same subroutine *f*. Consider the path  $C1 \rightarrow IN \rightarrow EX \rightarrow R2$ . This path returns to the wrong call site and hence

does not occur in any execution. But since variable  $s_2$  is used in  $R_2$  and not defined along the path we conclude that  $s_2$  is live at  $C_1$ , while in fact  $s_2$  is dead, as it is defined in  $R_1$ .

Paths which do not return to the wrong call site are called *realizable paths*, e.g.,  $C1 \rightarrow IN \rightarrow EX \rightarrow R1$  or  $C2 \rightarrow IN \rightarrow EX \rightarrow R2$ . See [46] for a more rigorous definition.

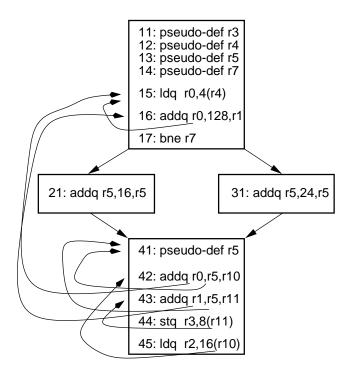

Figure 3.1: Unrealizable path in context insensitive analyses

A context sensitive interprocedural data flow analysis considers only realizable paths in the interprocedural control flow graph [52].

### 3.1.2 Interprocedural Register Liveness Analysis

In this section we discuss two flavors of interprocedural liveness analysis: Context sensitive and context insensitive. Tuning possibilities are described and performance numbers presented.

#### 3.1.2.1 Context Insensitive Analysis

As described in the previous section, the context insensitive liveness analysis uses the standard intraprocedural analysis [55] and applies it to a program's interprocedural control flow graph treating *call* and *return* edges as ordinary edges, and ignoring *link* edges.

The analysis iteratively computes the fixpoint of the equations below

$$LiveIn[n] = use[n] \cup (LiveOut[n] - def[n]) \quad n \in Nodes$$

$LiveOut[n] = \bigcup s \in Succ[n] : LiveIn[s]$   $n \in Nodes$ subject to the initial values

LiveOut[n] :=  $\emptyset$   $n \in Nodes$ LiveIn[n] :=  $\emptyset$   $n \in Nodes$

$\mathcal{R}$  denotes the set of all registers. For each node *n*, *LiveIn*[*n*] (*LiveOut*[*n*]) contains the registers live at the beginning (end) of the node, *def*[*n*] contains the registers which are defined in *n*, *use*[*n*] contains the registers which are used before they are defined in *n*.

#### 3.1.2.2 Context Sensitive Analysis

For context sensitive liveness analysis we must restrict ourselves to realizable paths through the interprocedural control flow graph. This is achieved by considering intraprocedural paths only and modeling subroutine calls using summary information for the called subroutine [52]. Conceptually, all *call* and *return* edges are removed from the interprocedural control flow graph. Data flow through *link* edges is subject to modifications described by the summary information for the called subroutine.

Two pieces of information are necessary to summarize the effects of each subroutine f on liveness:

MayUse[f]. The set of registers that may be used by f. A register r may be used by f if there is a realizable path from InitNode[f] to a use of r without an intervening definition of r. MayUse[f] hence describes the set of registers which are live at the

beginning of InitNode[f] independent of the calling context and hence are live at the end of any *call* node  $n_c$  calling f. Typically these are the registers which are used to pass arguments to subroutine f.

• *ByPass*[*f*]. The set of registers which if live at *n<sub>r</sub>* are live at *n<sub>c</sub>* for any *call* node *n<sub>c</sub>* calling *f*. Typically these are the register which are not used at all by *f*.

We also define

- *MustDef*[*f*]. The set of registers which are defined (written to) on all paths from *InitNode*[*f*] to *ExitNode*[*f*].

- MustDead[f]. The set of registers which are defined on all paths from InitNode[f] to ExitNode[f] and are not used before they are defined. Clearly, MustDead[f] = MustDef[f] - MayUse[f]

Once *ByPass* and *MayUse* information has been computed for each subroutine, liveness information is computed as follows:

## Phase Live : Computation of LiveIn and LiveOut:

iteratively compute the fixpoint of the data flow equations listed below

$$\begin{split} LiveIn[n] &= use[n] \cup & n \in Nodes \\ & (LiveOut[n] - def[n]) \\ LiveOut[n] &= \bigcup s \in Succ[n] : & n \in Nodes \land Type[n] \notin \{call\} \\ & LiveIn[s] \\ &= MayUse[f] \cup & n \in Nodes \land Type[n] = call \land \\ & (ByPass[f] \cap LiveIn[n']) & n' = ReturnNode[n] \land f = Callee[n] \end{split}$$

subject to the initial values

| LiveOut[n] | $:= \emptyset$                        | $n \in Nodes$     |

|------------|---------------------------------------|-------------------|

| LiveIn[n]  | $:= \emptyset$                        | $n \in Nodes$     |

| MayUse[f]  | := as computed by Phase <i>MayUse</i> | $f \in Functions$ |

| ByPass[f]  | := as computed in Phase <i>ByPass</i> | $f \in Functions$ |

The important aspect is the computation for the *call* nodes. A register is live at the end of a *call* node if the register is used by the callee (*MayUse* case) or it is live at the corresponding *return* node and not defined — on at least one realizable path — inside of the callee (*ByPass* case). This gives us some choice in the selection/computation of the *ByPass* sets. If a register is in *MayUse*[f] we can include it in *ByPass*[f] even if the register is never live at any of the corresponding *return* nodes. Srivastava *et al.* [67] choose *ByPass*[f] to be  $\overline{MustDead}[f]$ . The problem with this approach is that it introduces a mutual dependency between *ByPass* information and *MayUse* information which complicates the flow equations. Goodwin [36] chooses *ByPass*[f] to be  $\overline{MustDef}[f]$  which does not have this problem and is therefore preferable. In fact, any set which lies between  $\overline{MustDef}[f]$  and  $\overline{MustDef}[f] \cup MayUse[f]$  is a valid candidate for ByPass[f]. Our choice for ByPass[f] is a superset of Goodwin's <sup>1</sup> and will result in more uniform data flow equations. Below we show how the *ByPass* and *MayUse* sets are computed.

## **Phase** MayUse : Computation of MayUse[f] :

iteratively compute the fixpoint of the data flow equations listed below

<sup>&</sup>lt;sup>1</sup>it is difficult to give more intuitive description for this choice other than the fixpoint equations

$$\begin{array}{ll} MayUseIn[n] &= use[n] \cup & n \in Nodes \\ & (MayUseOut[n] - def[n]) \\ MayUseOut[n] &= \bigcup s \in Succ[n] : & n \in Nodes \land Type[n] \notin \{call, exit\} \\ & MayUseIn[s] \\ &= MayUse[f] \cup & n \in Nodes \land Type[n] = call \land \\ & (ByPass[f] \cap MayUseIn[n']) & n' = ReturnNode[n] \land f = Callee[n] \\ MayUse[f] &= MayUseIn[InitNode[f]] & f \in Functions \end{array}$$

subject to the initial values

| MayUseOut[n] | $:= \emptyset$                        | $n \in Nodes$     |

|--------------|---------------------------------------|-------------------|

| MayUseIn[n]  | $:= \emptyset$                        | $n \in Nodes$     |

| MayUse[f]    | $:= \emptyset$                        | $f \in Functions$ |

| ByPass[f]    | := as computed in Phase <i>ByPass</i> | $f \in Functions$ |

# **Phase** ByPass : Computation of <math>ByPass[f]:

iteratively compute the fixpoint of the data flow equations listed below

Subject to the initial values

Contrary to the intraprocedural liveness analysis or the context insensitive analysis the choice of the starting values is crucial, e.g., initializing ByPassOut[f] of non-*exit* nodes to  $\mathcal{R}$  as in [36] yields overly conservative results [37]. Differing from Goodwin's approach we have modified the equation for ByPassIn[n] by adding (unioning) use[n]to the right hand side. This makes our ByPass sets strictly bigger than his but since  $use[n] \subseteq MayUseIn[n]$  holds, ByPassIn[InitNode[f]] will still lie between  $\overline{MustDef}[f]$ and  $\overline{MustDef}[f] \cup MayUse[f]$ . The major virtue of this change is that it makes the equations of the three phases sufficiently similar that they can be unified into just one simple and compact set of equations (cf. Figure 3.2). The code implementing the analysis, which uses the unified equations by means of a subroutine call is also correspondingly simpler and smaller. The bigger sets do not affect the performance if they are realized as bit vectors.

|                                             |      |                  | Unif | ied Dataf            | low ]   | Equations:        |                                            |           |  |

|---------------------------------------------|------|------------------|------|----------------------|---------|-------------------|--------------------------------------------|-----------|--|

| DataIn[n]                                   | = u  | $se[n] \cup (a)$ | Data | Out[n] - a           | lef[n   | $n])  n \in Node$ | es                                         |           |  |

| DataOut[n]                                  | = L  | $Js \in Suc$     | c[n] | : DataIn[s]          |         | $n \in Nod$       | $n \in Nodes \land Type[n] \notin NoTypes$ |           |  |

|                                             | = M  | layUse[j         | f]∪( | [ByPass[f]           | $\cap$  | $n \in Nod$       | $es \wedge Type[n]$                        | a] = call |  |

| DataIn[ReturnNode[n]])                      |      |                  |      |                      |         |                   |                                            |           |  |